### <sup>09/2014</sup> Dual Selectable Low Voltage Lowpass/Bandpass Filter Data Sheet

### Description-

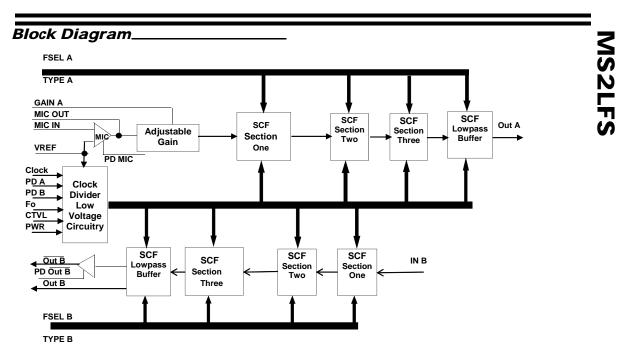

The dual selectable lowpass/bandpass filter IC is a CMOS chip that can be configured for either a lowpass or a bandpass filter. Each filter is selectable independently. The lowpass response can be a 7 pole Butterworth, Elliptic or Bessel filter. The band pass response can be a six pole full, third or sixth octave bandpass filter. The device uses switchedcapacitor filters and no external components (except for decoupling capacitors) are required, Only an external CMOS level clock is needed.

An externally selectable gain setting pin, a power down pin and clock to corner ratio select pin are included. Typical current consumption is as low as 500 uA and the minimum operating voltage is 1.1 volts, making the device ideal for portable applications.

#### Features-

Two Independent Filters Six Filter Types In One Package No External Components Switched-Capacitor Filters Low Power Operation Low Voltage Operation Adjustable Gain 0, 6 or 12 dB Small Package Size Low Cost On Chip Power Save Pin ANSI Compatible Bandpass Op Amp Input **MS2LFS**

### **Applications**

Spectrum Analyzers Battery powered General Purpose Systems Portable Systems Anti-Alias Filters Reconstruction Filters Telecommunications (Cell phone ASP) Tracking Filters Harmonic Analysis Noise Analysis Data Communication Wireless Applications Telemetry

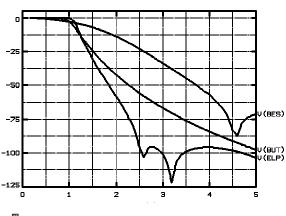

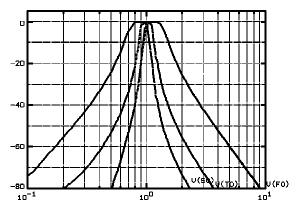

**Lowpass Responses**

Web Site "www.mix-sig.com"

**Bandpass Responses**

© 2000-2014 Mixed Signal Integration 1

# Dual Selectable Low Voltage Lowpass/Bandpass Filter

| PARAMETER                         | SYMBOL | CONDITIONS                       | MIN   | TYP   | MAX  | UNITS  |

|-----------------------------------|--------|----------------------------------|-------|-------|------|--------|

| DC Specifications                 |        |                                  |       |       | 1    |        |

| Operating Voltage                 | VDD    |                                  | 1.1   | 1.2   | 3.6  | V      |

| Supply Current                    | IDD    | VDD = 3.3V, CTVL = 0,<br>PWR = 1 |       | 2.7   |      | mA     |

| Supply Current                    | IDD    | VDD = 1.1V, CTVL = 1,<br>PWR = 1 |       | 1100  |      | uA     |

| Supply Current Low Power<br>Mode  | IDD    | VDD = 3.3V, CTVL = 0,<br>PWR = 0 |       | 1     |      | mA     |

| Supply Current Low Power<br>Mode  | IDD    | VDD = 1.1V, CTVL = 1,<br>PWR = 0 |       | 200   |      | uA     |

| Supply Current Power Down<br>Mode | IDD    | PDA=PDB=0, CTVL=0                |       | 50    |      | uA     |

| AC Specifications                 | •      | •                                |       |       |      |        |

| Gain                              | Av     |                                  | -0.5  | 0     | 0.5  | dB     |

| Noise                             |        | To 1/2 Sample                    |       | 200   |      | uVrms  |

| Distortion                        | THD    |                                  |       | -62   |      | dB     |

| Signal Swing                      |        | 1 kHz, VDD = 1.2V                | 800   |       |      | mV p-p |

| Input Impedance                   | ZIN    |                                  |       | 1     |      | Mohm   |

| Output Drive                      | lo     |                                  |       | 1     |      | mA     |

| Output Impedance                  | Zo     |                                  |       | 500   |      | ohm    |

| Output Capacitive Load            |        |                                  |       | 22    |      | pF     |

| Clock to Corner *                 |        | Fo=1                             |       | 85.3  |      | Hz/Hz  |

| Clock to Corner *                 |        | Fo=0                             |       | 42.65 |      | Hz/Hz  |

| Center Frequency Range            | Fo     |                                  | 0.001 |       | 6    | kHz    |

| Ripple                            |        |                                  |       |       |      |        |

| Elliptic Lowpass                  |        |                                  |       | 0.2   |      | dB     |

| Full Octave                       |        |                                  |       | 0.2   |      | dB     |

| Third Octave                      |        |                                  |       | 0.2   |      | dB     |

| Sixth Octave                      |        |                                  |       | 0.2   |      | dB     |

| Stop Band Rejection               |        |                                  |       |       |      |        |

| Elliptic/Butterworth Lowpass      |        | fCLOCK = 2.048 MHz               |       | 75    |      | dB     |

| Bessel Lowpass                    |        | fCLOCK = 2.048 MHz               |       | 65    |      | dB     |

| 40 dB Bandwidth                   |        |                                  |       |       |      |        |

| Full Octave                       |        | Normalized Fo                    | 0.3   |       | 3    |        |

| Third Octave                      |        | Normalized Fo                    | 0.6   |       | 1.67 |        |

| Sixth Octave                      |        | Normalized Fo                    | 0.76  |       | 1.32 |        |

| Bandpass Q                        | -      | ·                                |       |       |      | -      |

| Full Octave Q                     | Q      |                                  |       | 1.5   |      |        |

| Third Octave                      | Q      |                                  |       | 4.5   |      |        |

| Sixth Octave                      | Q      |                                  |       | 9     |      |        |

\* External clock is 8X internal clock

i≀ת≊

Web Site "www.mix-sig.com"

© 2000-2014 Mixed Signal Integration 2

**MS2LFS**

## Dual Selectable Low Voltage Lowpass/Bandpass Filter Data Sheet

| Pin Descri  | iption                                  | 21. TYPE B              | Filte          |

|-------------|-----------------------------------------|-------------------------|----------------|

| 1. IN B     | Filter Input B                          | 21. THE B<br>22. FO B   | Cloc           |

| 2. VDD      | Positive Power Supply, typically        |                         | for F          |

|             | 1.2 Volts for Single Supply             | 23. OUT B               | Filte          |

| 3. CTVL     | Activate or Disable Boost Circuit       |                         | 180<br>OUT     |

|             | Disable = 0, Activate = 1               | 24. FO A                | Cloc           |

| 4. PDA      | Power Down Filter A                     |                         | for F          |

| 5. PD MIC   | Power Down Mic Amp                      | 25. out B<br>26. gain a | Filte<br>Filte |

| 6. PD OUTB  | Power Down Output B                     | 27. PD B                | Pow            |

| 7. NC       |                                         | 28. FSEL B              | Sele           |

| 8. CLK      | Clock Input                             |                         | 0 =            |

| 9. NC       |                                         |                         |                |

| 10.PWR      | Sets Bias Current for Filter Stages     |                         |                |

|             | Lo=low power, Hi=normal power           | Pin Config              | gura           |

| 11. NC      |                                         | <b></b>                 |                |

| 12. OUT A   | Filter Output A                         | 1                       |                |

| 13. BYP     | Bypass Capacitor for Boost Circuit,     |                         |                |

|             | voltage at this pin is negative in      | DD                      |                |

|             | relation to VSS, tie positive side of   | СтуL                    |                |

|             | polarized cap to VSS                    | 4 PDA                   |                |

| 14. VSS     | Ground Pin, 0 Volts                     | 5 PDMIC                 |                |

|             | for Single Supply                       | 1.2                     |                |

| 15. TYPE A  | Filter Response Select Pin for Filter A |                         |                |

| 16. GND1    | AC Ground, decouple with 0.1 uF to      | -7 NC7                  |                |

|             | VSS                                     |                         |                |

| 17. VREF    | Reference Voltage, internally           | 9 NC9                   |                |

|             | generated, typically VDD/2.2 for        | 10 PWR                  |                |

|             | Single Supply Operation, decouple       | 1 1                     |                |

|             | with 0.1 uF to VSS                      | 12                      |                |

| 18. MIC IN  | Input of MIC Amp                        |                         |                |

| 19. MIC OUT | Output to MIC Amp                       | 13 BYP                  |                |

| 20. FSEL A  | Selects Filter.                         | 14<br>VSS               |                |

|             | 0 = Low Pass, 1 = Band Pass             |                         |                |

|             |                                         | 1                       |                |

| 21. TYPE B | Filter Response Select Pin for Filter B | $\leq$ |

|------------|-----------------------------------------|--------|

| 22. FO B   | Clock to Corner Select Pin              | n      |

|            | for Filter B                            | -      |

| 23. OUT B  |                                         |        |

|            | 180 degrees out of phase from           |        |

|            | OUT B                                   |        |

| 24. FO A   | Clock to Corner Select Pin              | n      |

|            | for Filter A                            |        |

| 25. OUT B  | Filter B Output                         |        |

| 26. gain a | Filter A, Gain Select Pin               |        |

| 27. PD B   | Power Down, Filter B                    |        |

| 28. FSEL B | Selects Filter                          |        |

|            | 0 = Low Pass, 1 = Band Pass             |        |

|            |                                         |        |

### ration

| _1               | INB     | FSELB              |

|------------------|---------|--------------------|

| _2               | YDD     | PD B27             |

| _3               | CTYL    | GAIN A26           |

| _4               | PDA     | OUT B              |

| _5               | PDMIC   | FO A <sup>24</sup> |

| ଆ ଏ ଏ ଅ ଅ ଅ<br>ଅ | PDOUTB* | OUTB*23            |

| _7               | NC7     | FO B22             |

| _8               | CLK     | TYPEB21            |

| 9                | NC9     | FSELA20            |

| 10               | PWR     | MIC OUT            |

| 11               | NC11    | MIC IN18           |

| <u>11</u><br>12  | OUTA    | VREF 17            |

| 13               | ВҮР     | GND1 16            |

| 14               |         | TYPE A 15          |

|                  | YSS     |                    |

|                  |         |                    |

∎N?i

Web Site "www.mix-sig.com"

© 2000-2014 Mixed Signal Integration 3

### Dual Selectable Low Voltage Lowpass/Bandpass Filter Data Sheet

### Absolute Maximum Ratings \_\_\_\_

| Power Supply Voltage  | +5V           |

|-----------------------|---------------|

| Storage Temperature   | -60 to +150 C |

| Operating Temperature | 0 to 70C      |

#### Ordering Information

Part NumberPackageMS2LFSP28 Pin DIPMS2LFSS28 Pin 300 mils wide SOIC

### Filter Selection\_

The filter type is selected using the two filter select pins, TYPE and FSEL, FSEL is a CMOS level pin that selects lowpass or bandpass (lowpass = 0, bandpass = 1). TYPE Is a tertiary control pin that selects the filter response. State 0 is VSS, state 1 is GND and state 2 is VDD.

|      | FSEL=0      | FSEL=1       |

|------|-------------|--------------|

| TYPE | Lowpass     | Bandpass     |

| 0    | Butterworth | Full Octave  |

| 1    | Bessel      | Third Octave |

| 2    | Elliptic    | Sixth Octave |

|      |             |              |

### **Digital Levels**

All the clock and control pins are referenced between VSS and VDD. In single supply applications, the digital levels should be CMOS levels from VSS to VDD. The tertiary controls (pins - TYPE and GAIN) should be set at VSS, VREF or VDD depending on the filter type or gain de-

### Gain and Frequency Selection\_\_\_\_

The Gain control pin G is a tertiary control pin where state 0 is VSS, state 1 is GND level and state 2 is VDD.

| G | Gain |

|---|------|

| 0 | OdB  |

| 1 | 6dB  |

| 2 | 12dB |

The frequency control pin F0 is a CMOS level pin where high is clock to corner of 85.3 to 1 (170.6 to 1 for Bessel) and low is clock to corner of 42.65 to 1 (85.3 to 1 for Bessel).

### ۳.۶i®

Web Site "www.mix-sig.com"

© 2000-2014 Mixed Signal Integration 4

Mixed Signal Integration Corporation reserves the right to to change any product or specification without notice at any time. Mixed Signal Integration products are not designed or authorized for use in life support systems. Mixed Signal Integration assumes no responsibility for errors in this document.

Dual Selectable Low Voltage Lowpass/Bandpass Filter Data Sheet

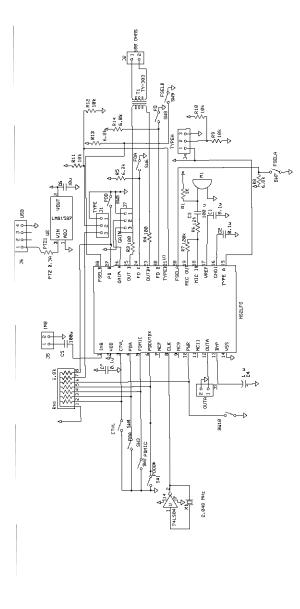

Application Schematic

**MS2LFS**

∎U?i

Web Site "www.mix-sig.com"